<u>Maika Takita</u>, Forrest Bradbury<sup>1</sup>, Stephen A Lyon Department of Electrical Engineering, Princeton University

Kevin Eng<sup>2</sup>, Tom M Gurrieri, Kathy J Wilkel, Malcom S Carroll Sandia National Laboratories

- 1. Present address: Amsterdam University College, Amsterdam, The Netherlands

- 2. Present address: HRL Laboratories, LLC, Malibu, CA, USA

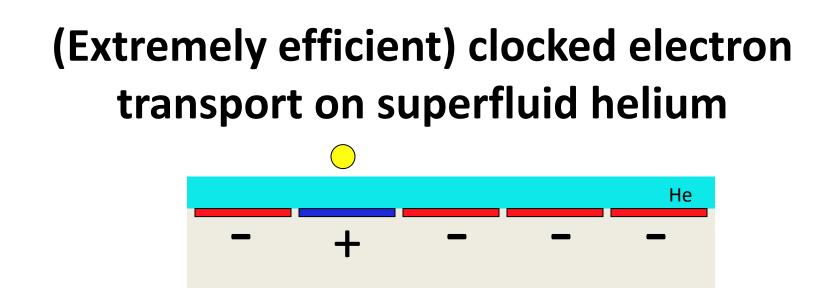

# Extremely efficient clocked electron transport on superfluid helium

## <u>Outline</u>

1. Intro

What can we do with mobile electrons?

2. Sandia Device

Clocking experiment

- 3. IBM Device

- What's next?

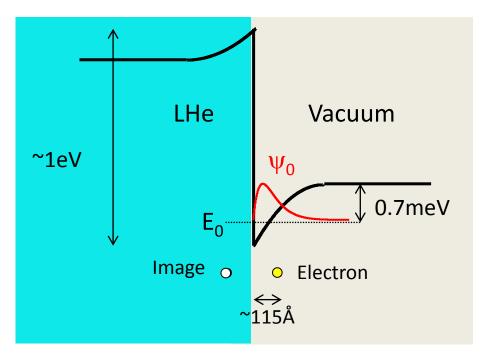

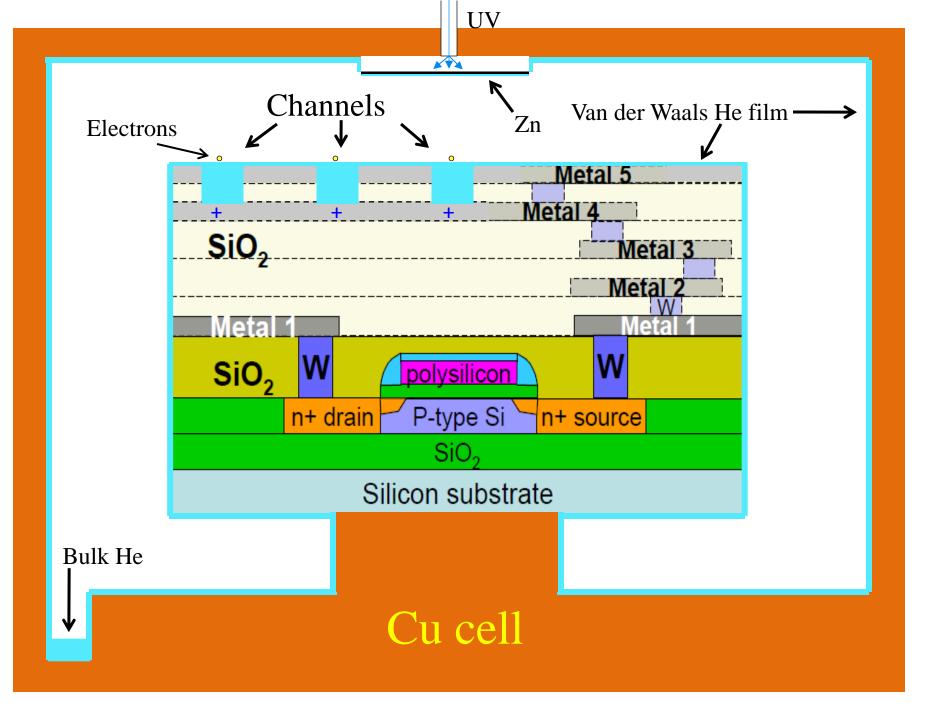

#### Electrons on superfluid helium

Clean system: Electrons in vacuum

Long spin coherence negligible spin-orbit interaction

$\Rightarrow$  Able to move electrons without spin decoherence!

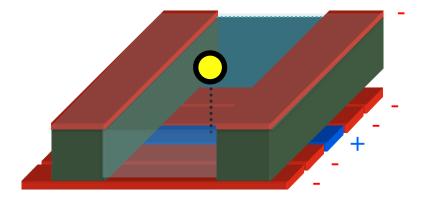

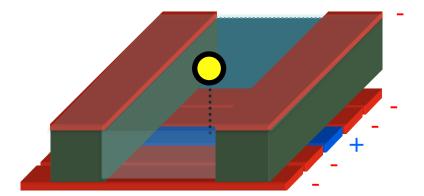

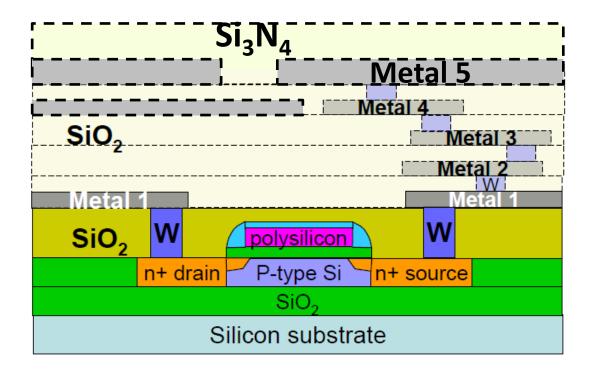

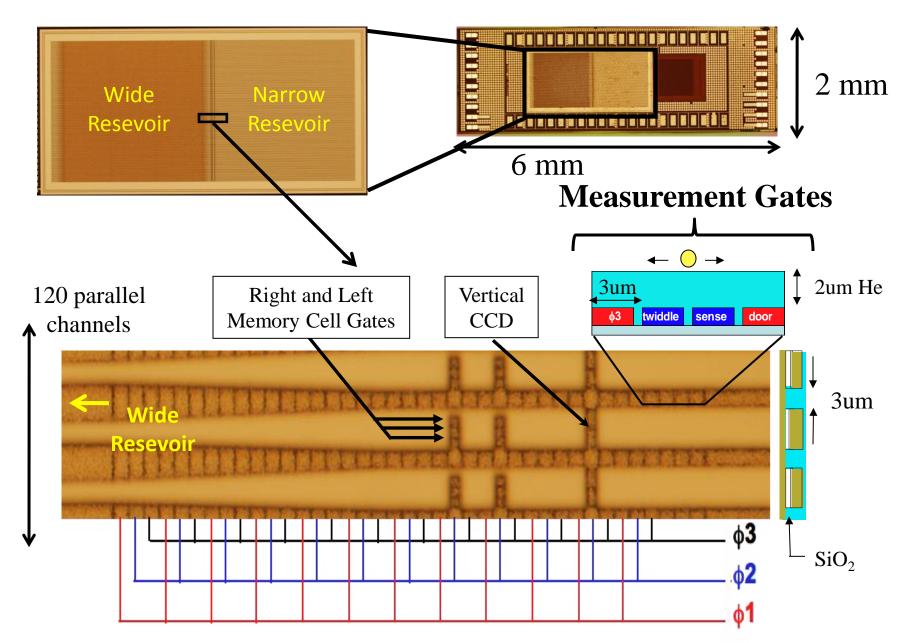

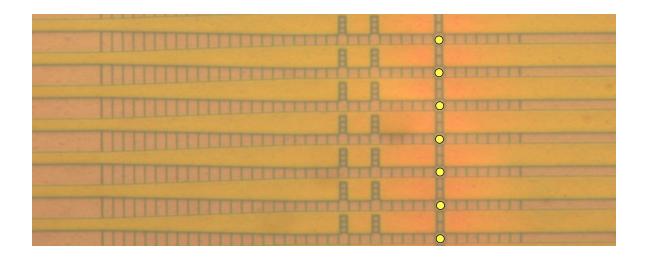

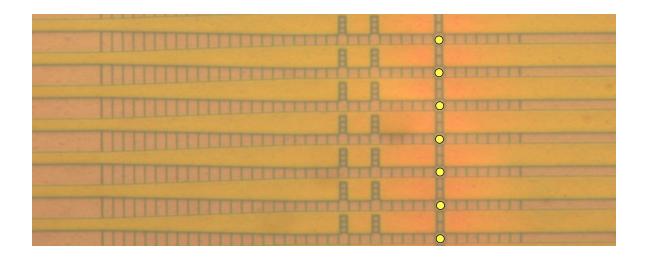

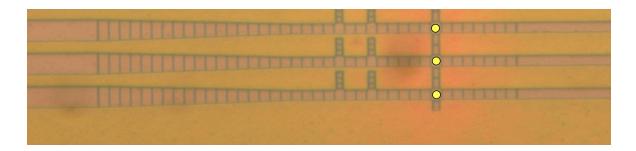

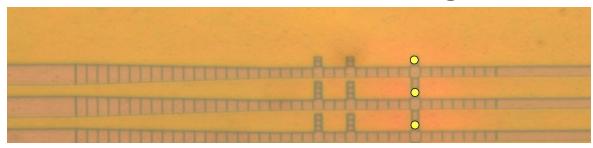

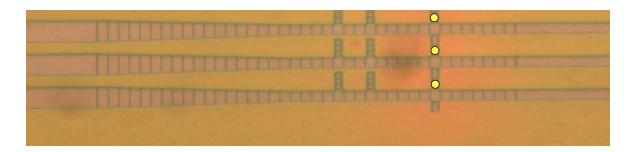

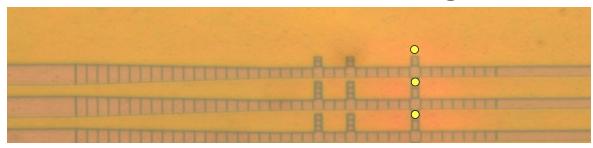

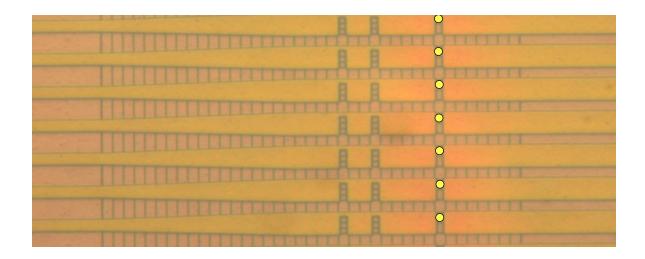

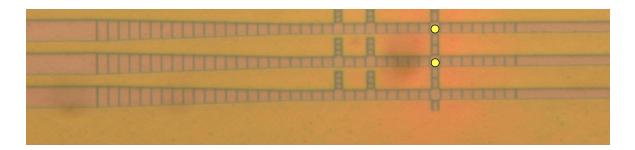

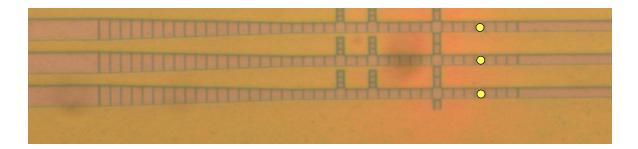

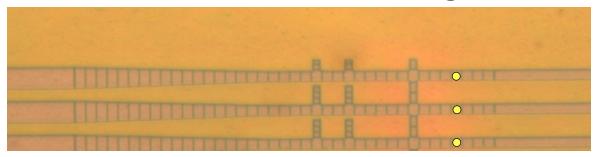

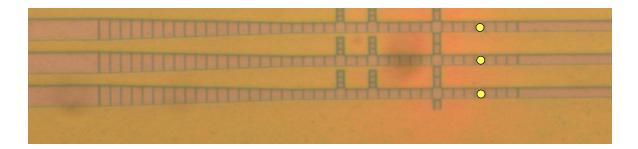

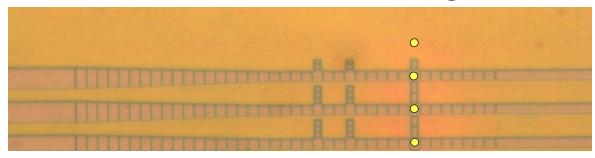

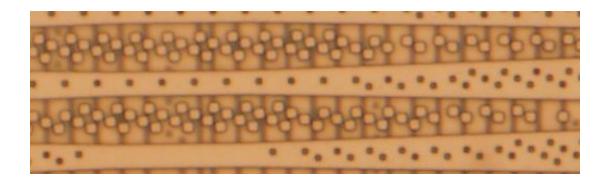

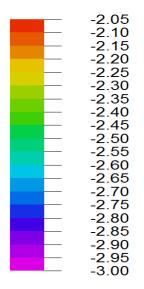

#### Channel Device with Sandia CMOS7

#### Channel Device with Sandia CMOS7

# Experiment

# Sandia Device

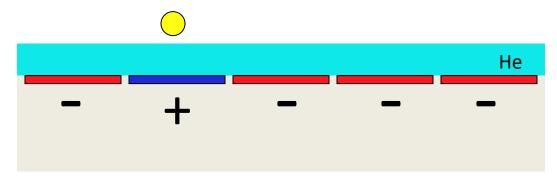

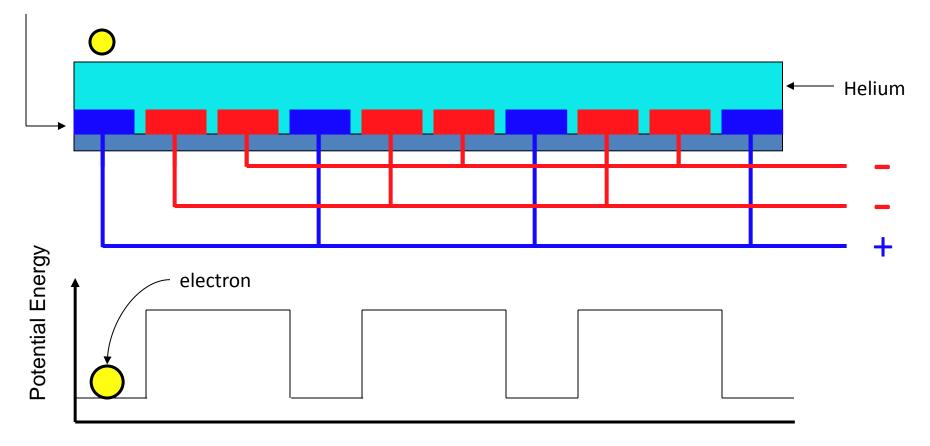

#### 3-phase CCD Potential

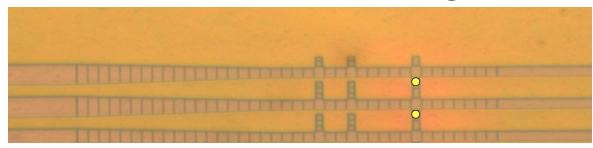

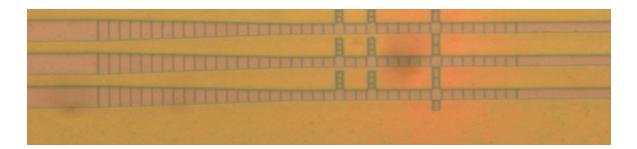

#### Underlying gates

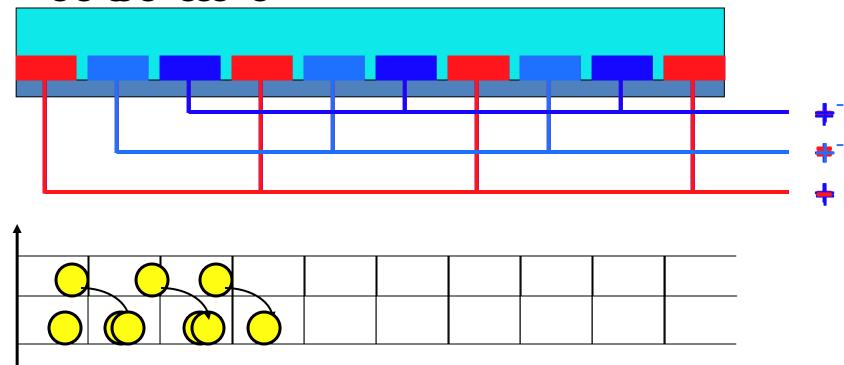

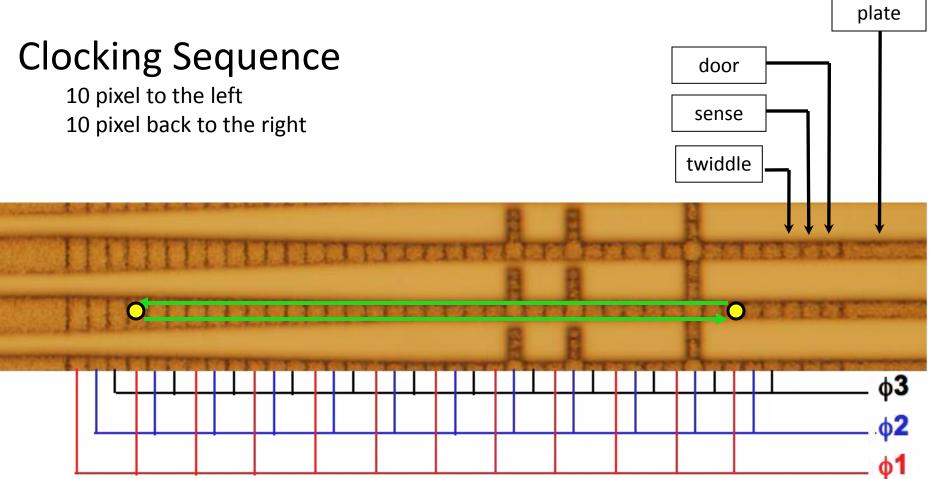

# 3-phase CCD

**Clocking** Electron has moved one pixel (3 gates) to the right

Potential Energy

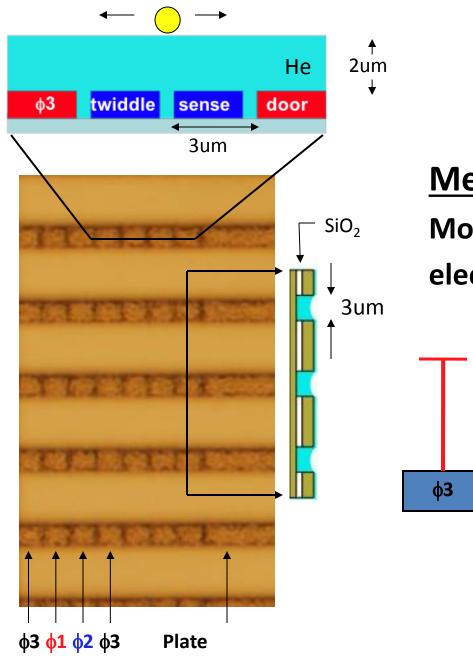

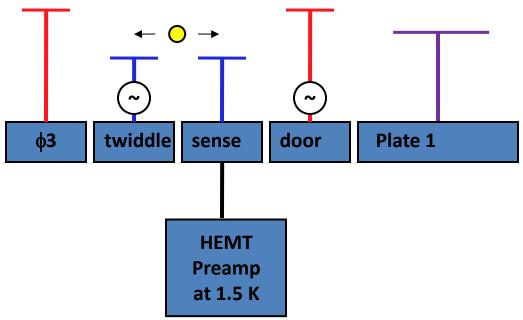

#### **Measurement**

Modulate twiddle to push electron on and off the sense gate

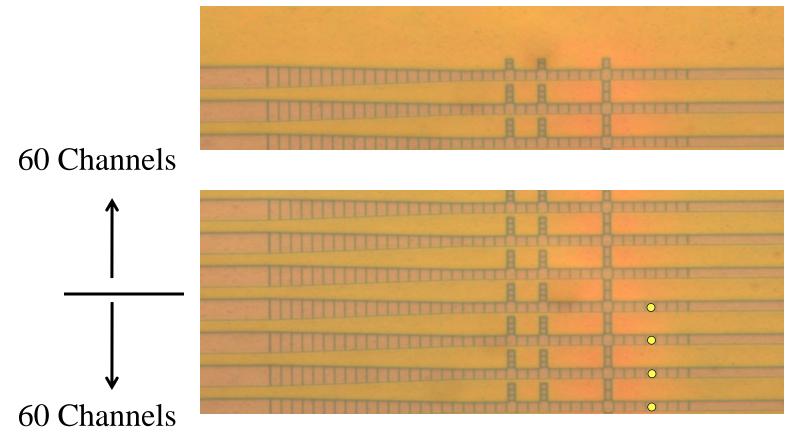

# Horizontal CCD

## Loading:

Photoemit electrons on plates Load them to pixels by opening the door

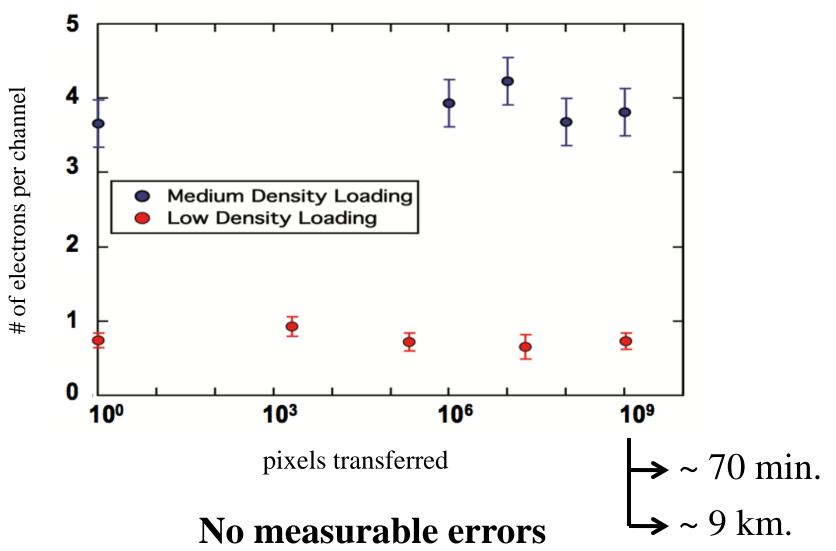

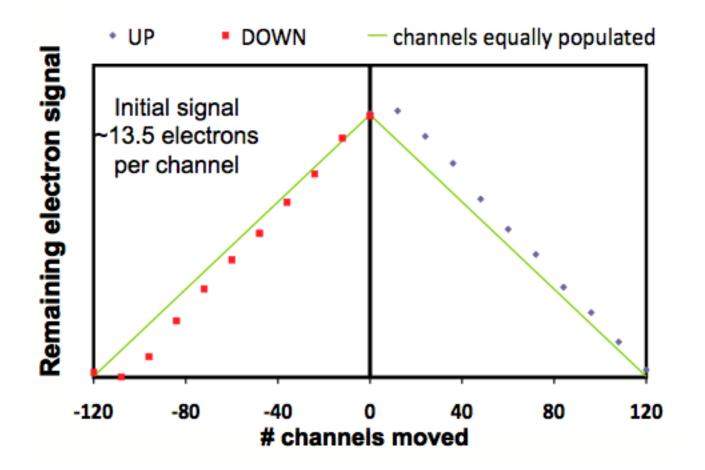

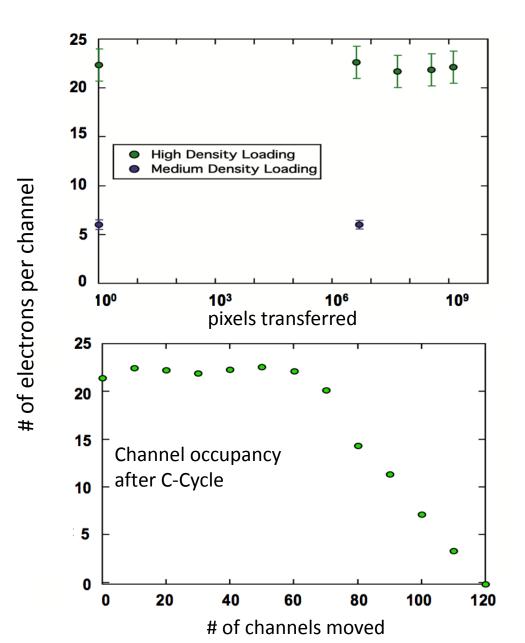

# **Horizontal Clocking Efficiency**

Clock (pixel) rate = 240kHz

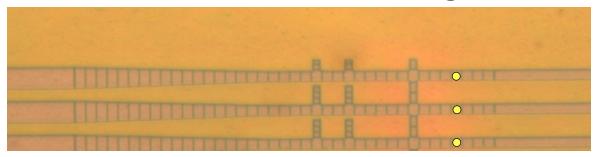

# **Channel Occupancy**

Vertical ("C-cycle") Efficiency

<u>Conclusions for electrons on superfluid helium channels with</u> <u>silicon integrated circuits (Sandia device)</u>

- •Unprecedented reliability of a Charge Coupled Device -Essentially a perfect Electron Transfer Efficiency

- 5 clock lines for full control

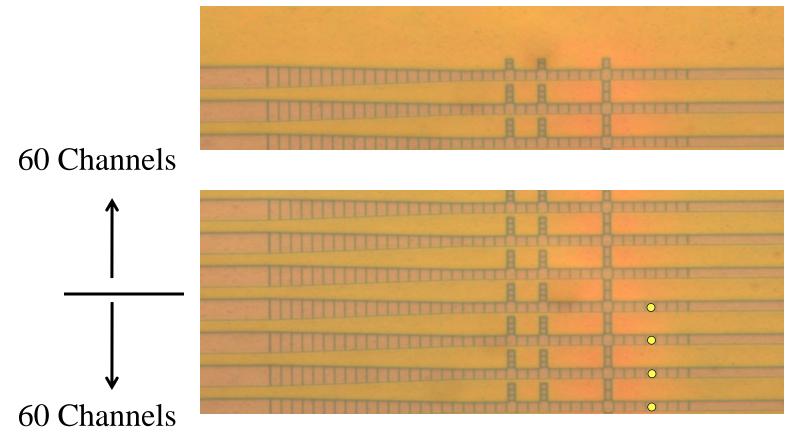

-2D Scalability: Move anywhere in our ~5000 position gate & channel array

- Si-Processing

- -First, non-optimized design with standard silicon processing

- -Possibilities for on-chip amplification

- -On-chip multiplexer

- -More...

Bradbury, Takita et al. PRL 107, 266803 (2011)

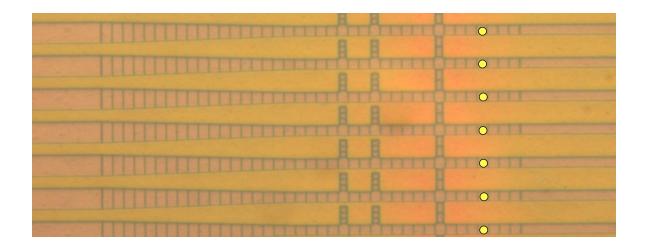

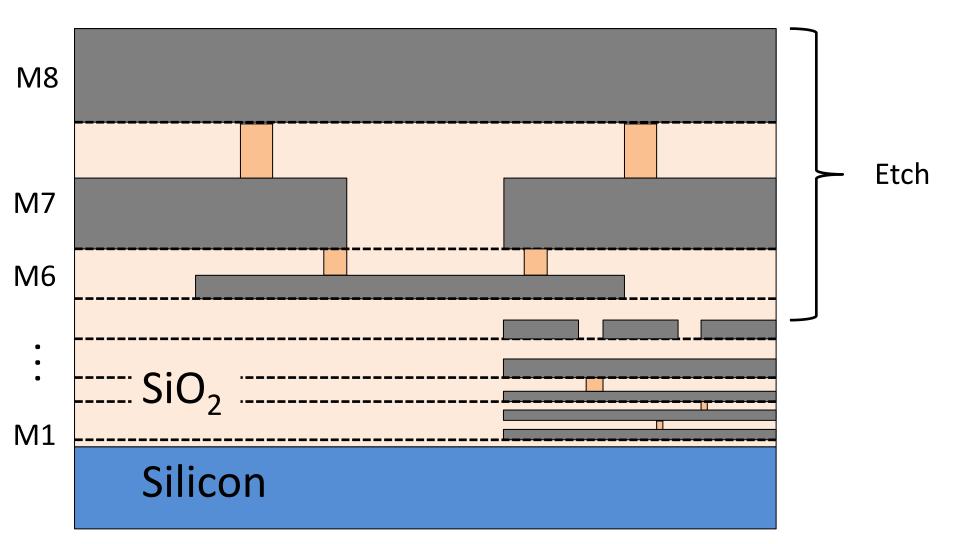

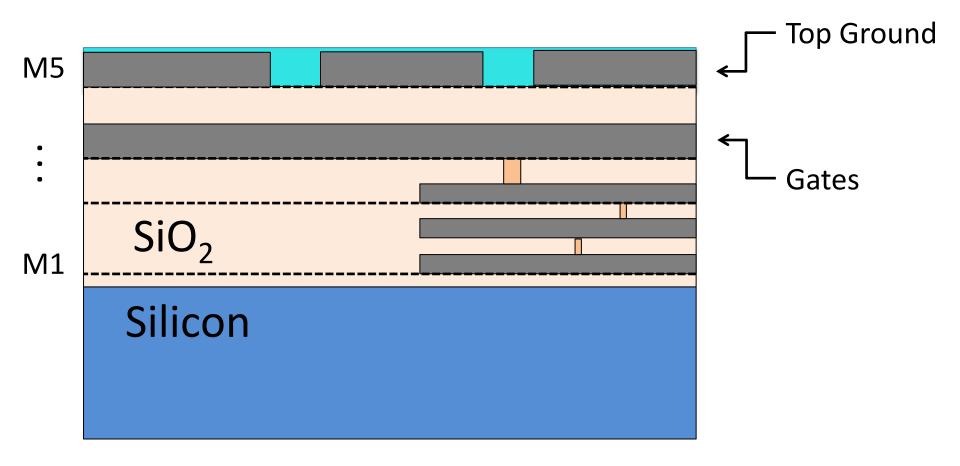

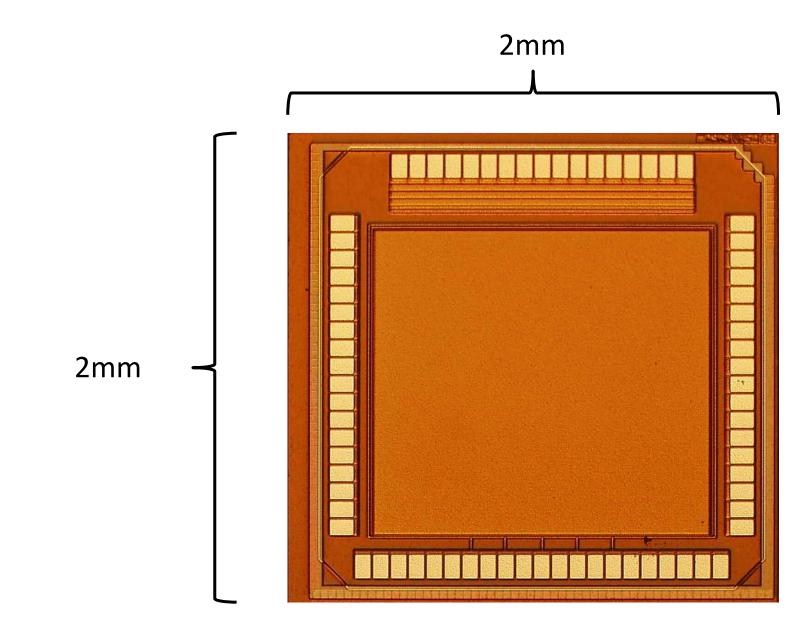

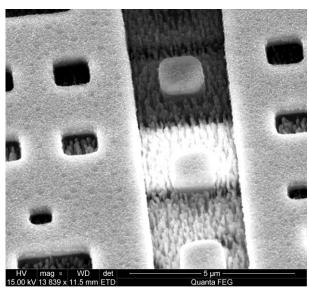

### 8 metal layers (Aluminum and Copper)

#### Channels using thin metals

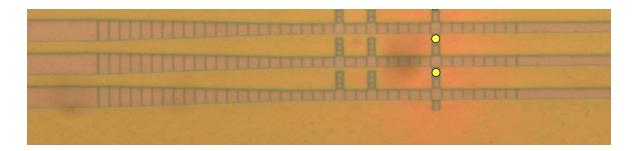

Filling and cheesing!!!!

Electroplating? Electro chemistry?

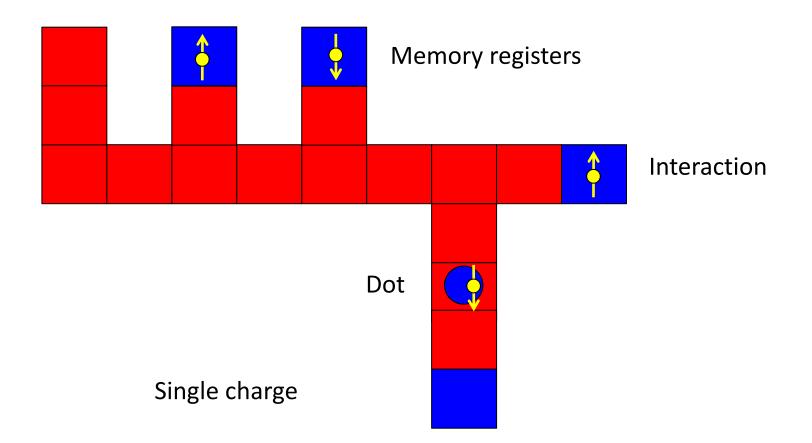

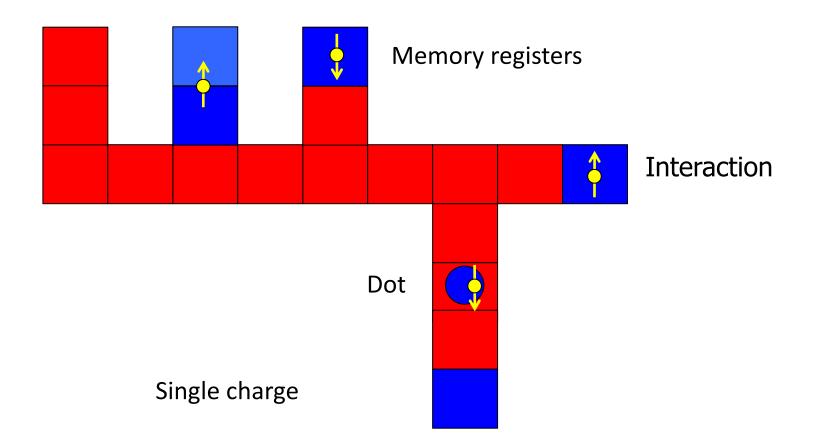

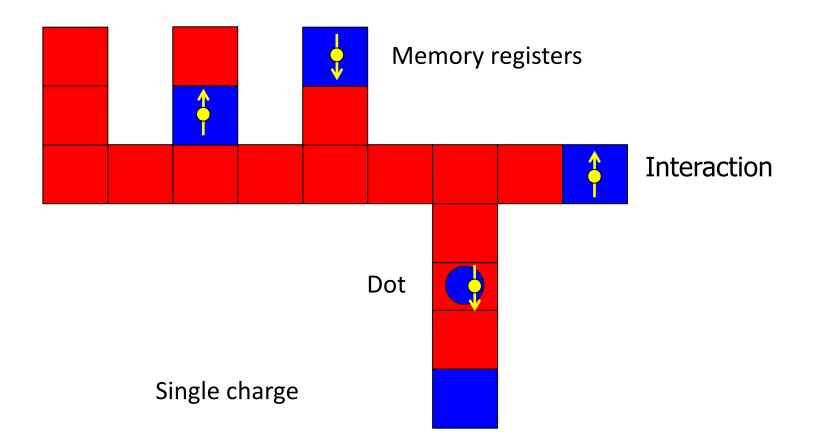

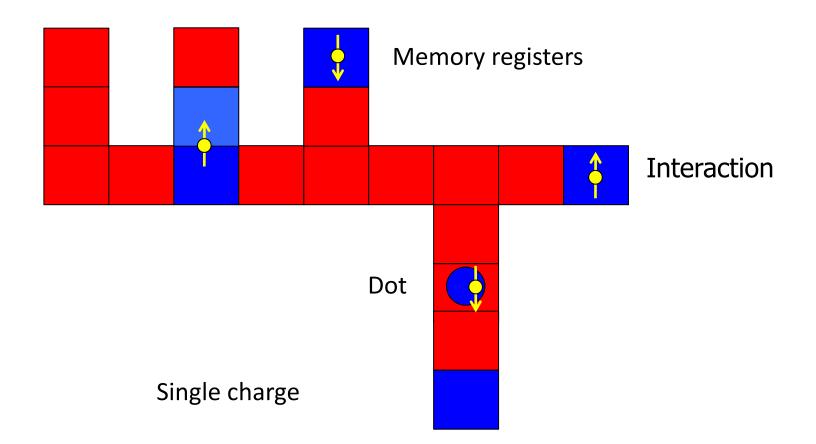

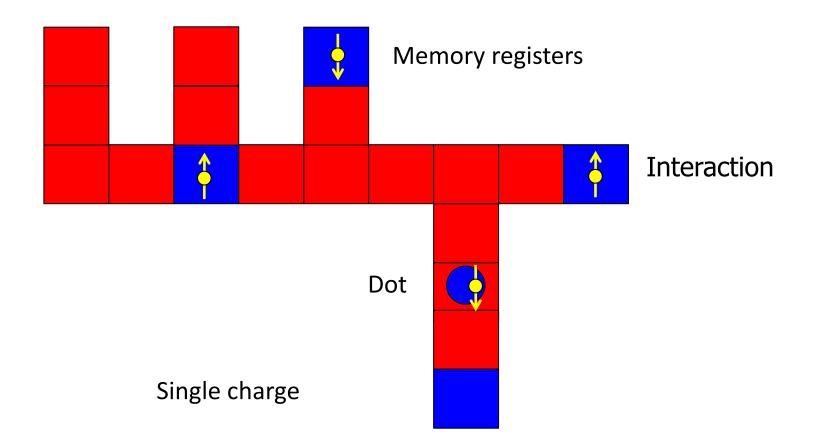

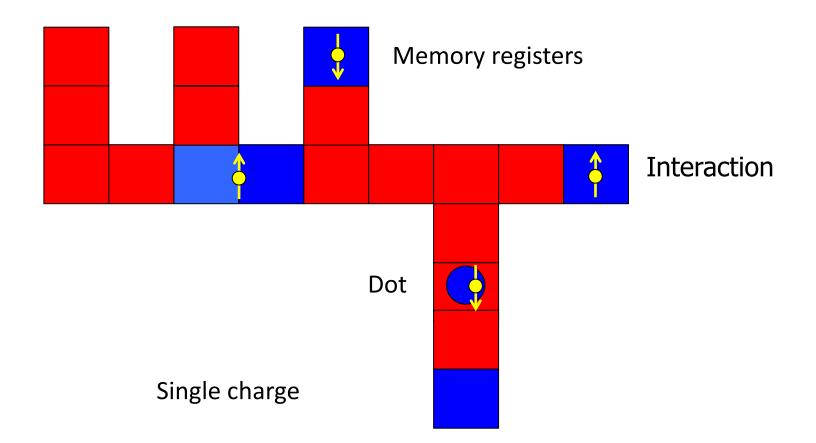

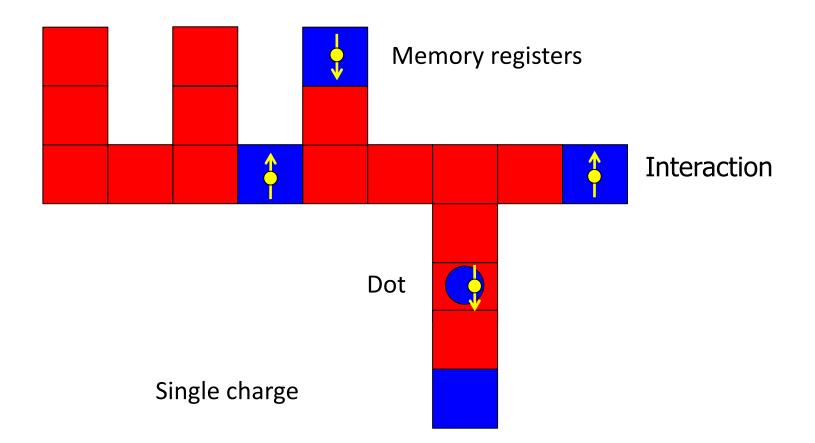

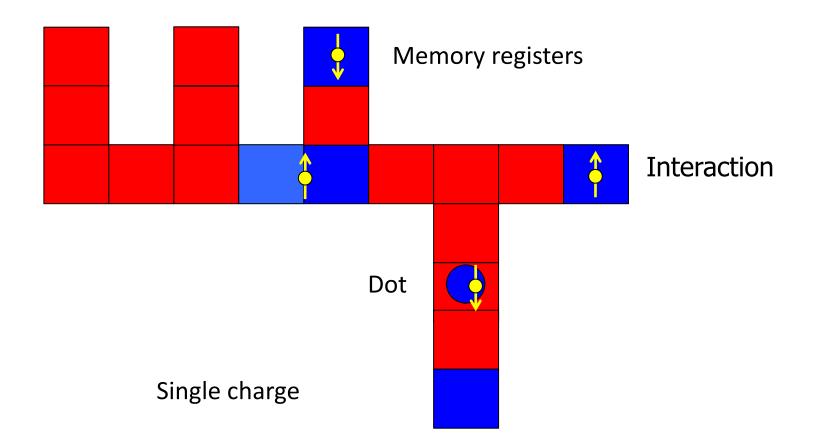

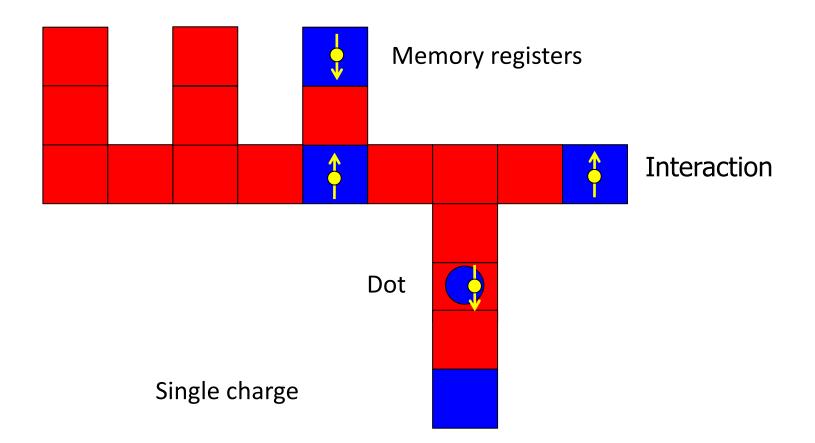

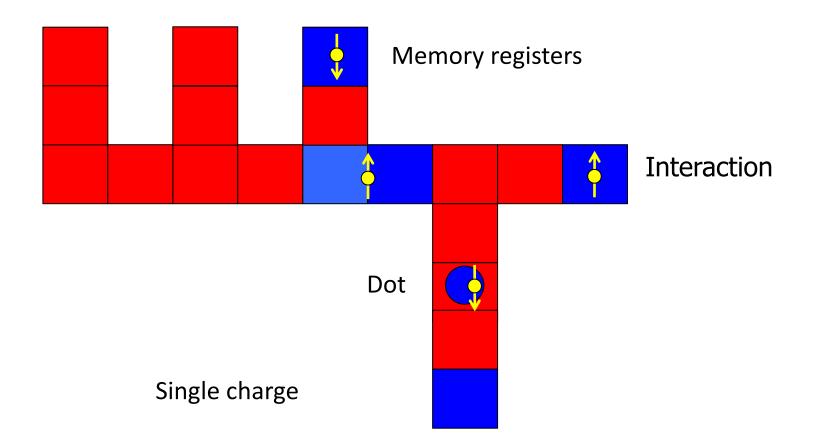

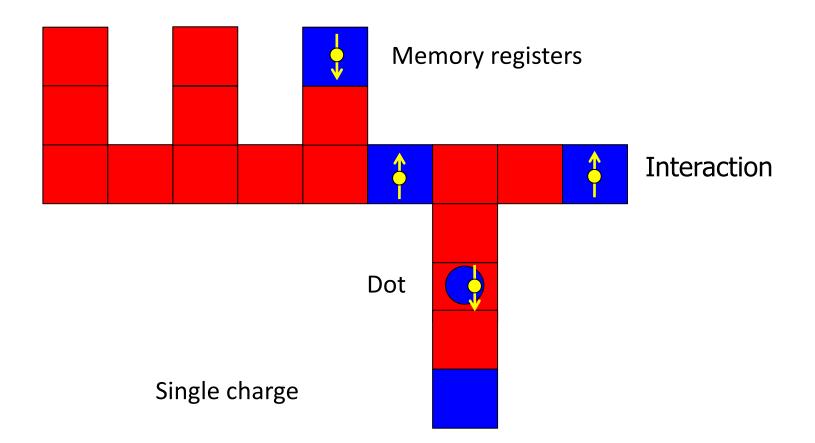

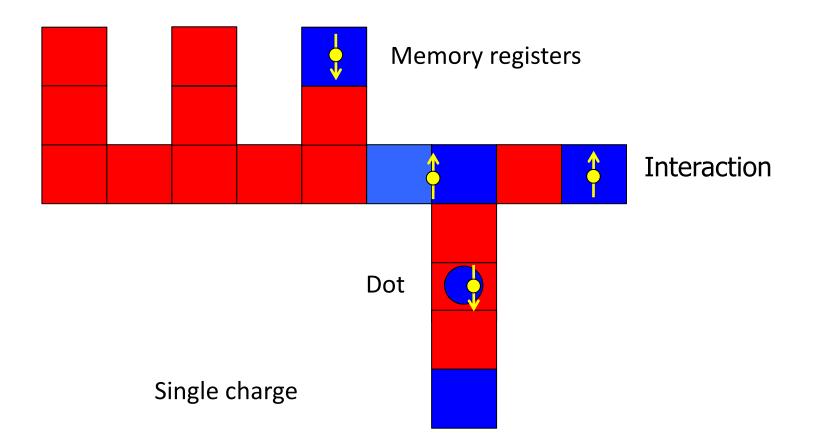

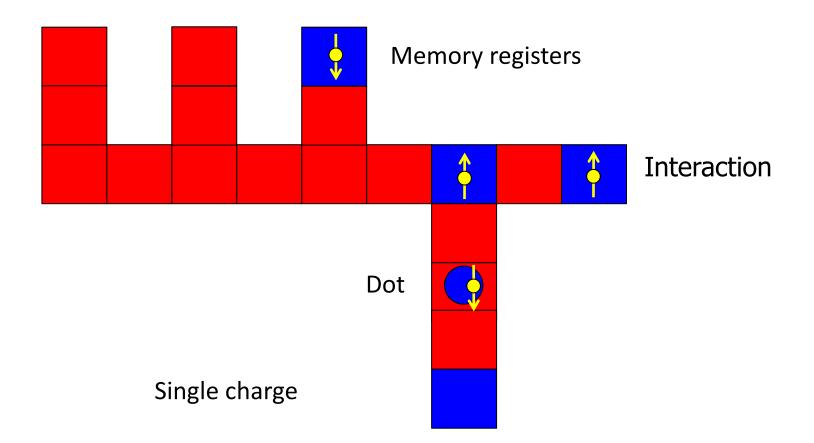

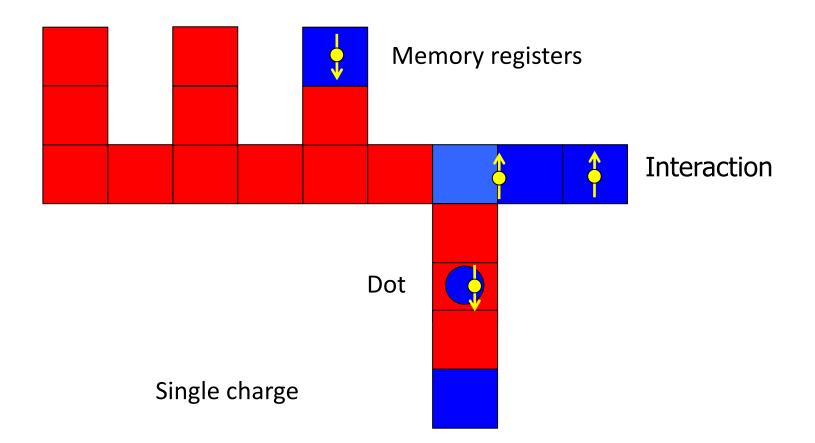

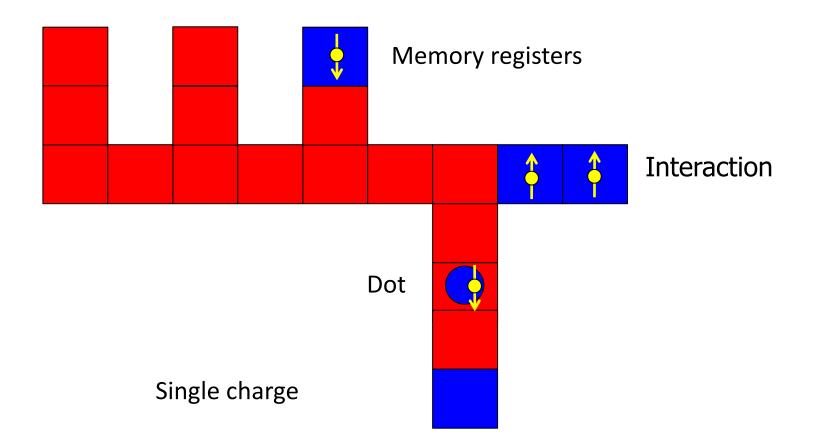

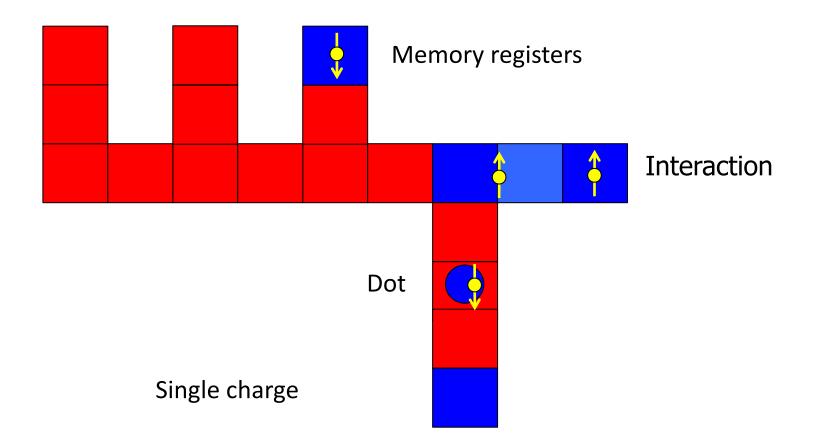

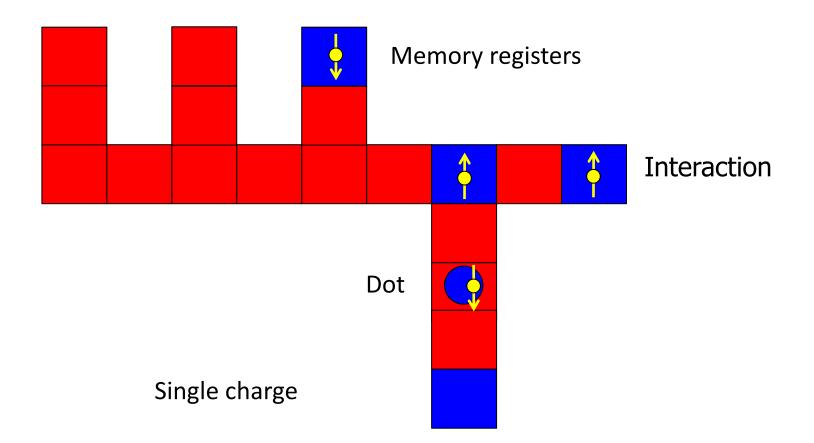

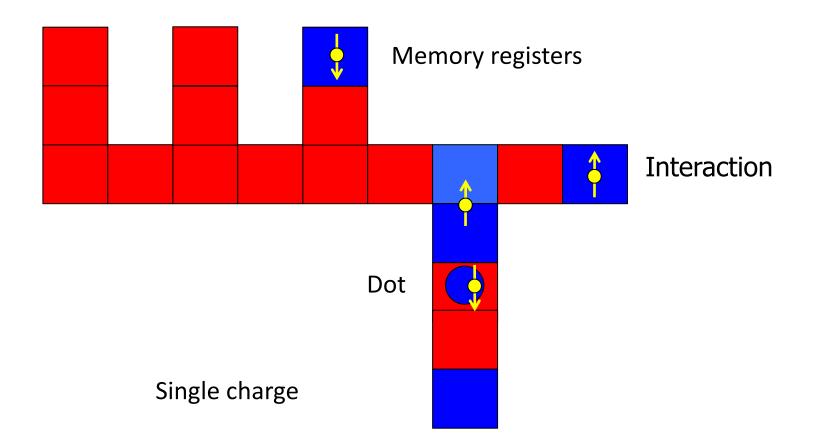

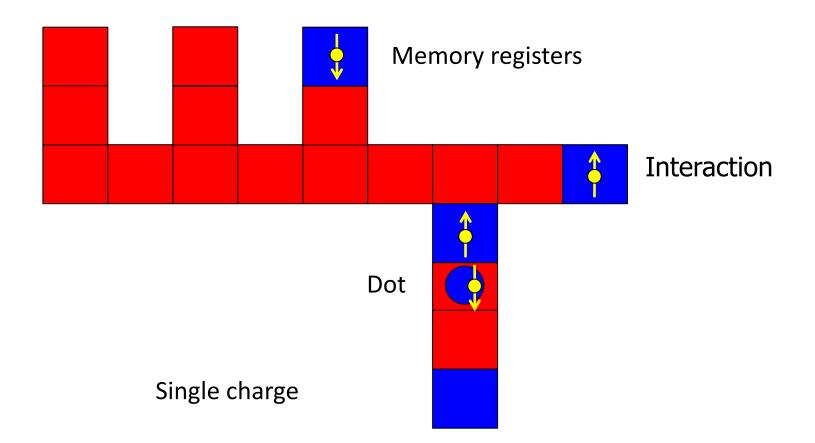

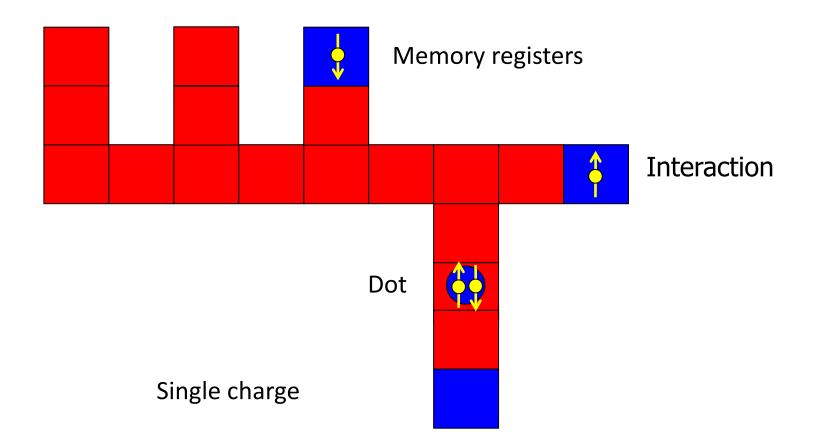

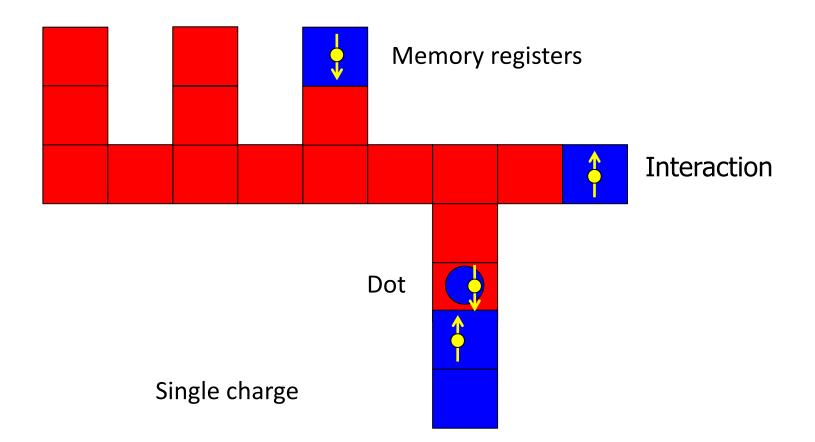

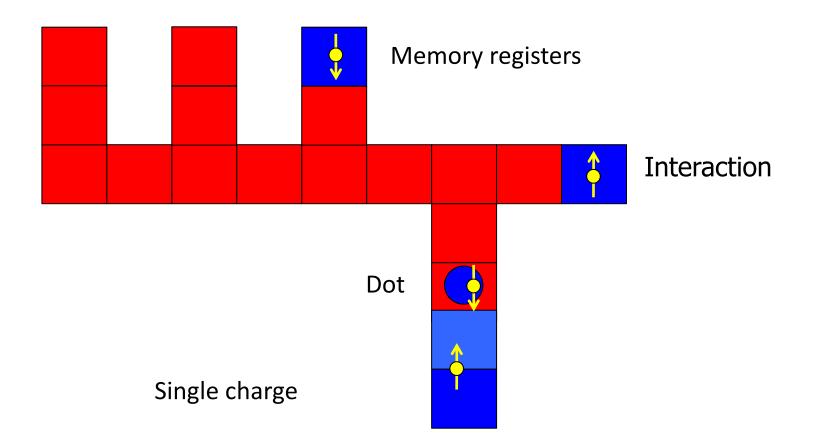

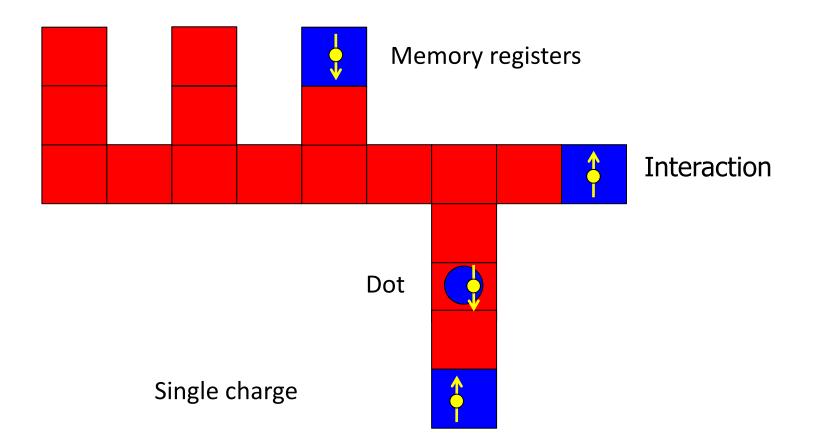

Turnstile Single Electron loading

- Turnstile

- Quantum dots

### **Need better sensing**

On-chip amplification? What else?

- Turnstile

- Quantum dots

### **Need better sensing**

On-chip amplification? What else?

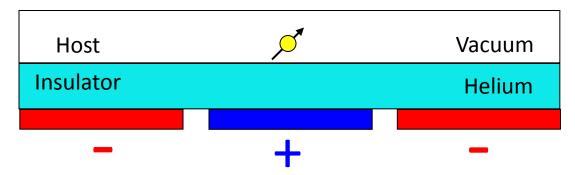

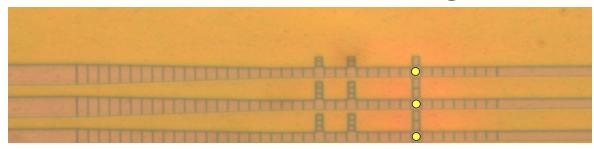

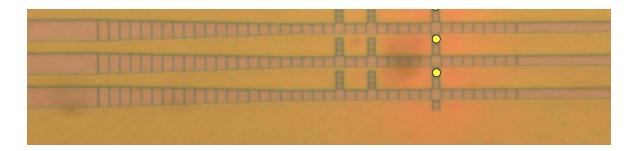

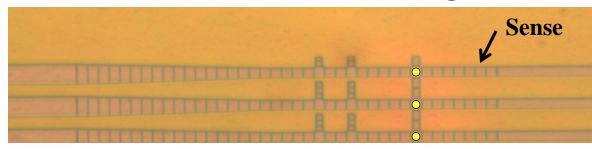

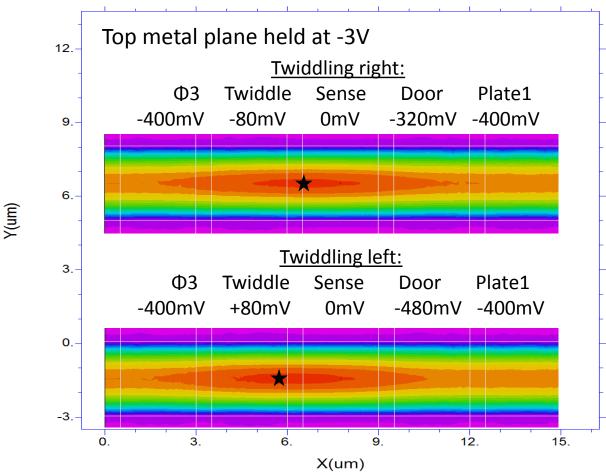

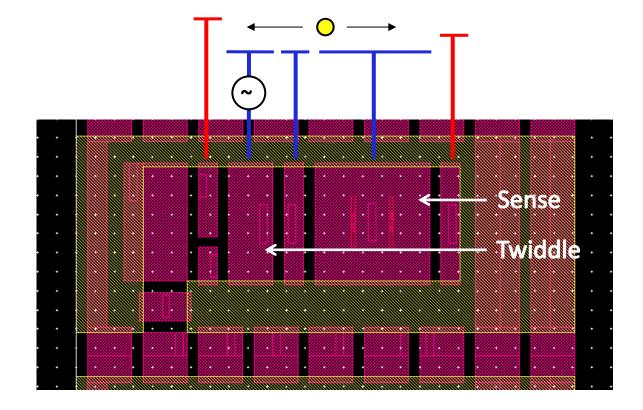

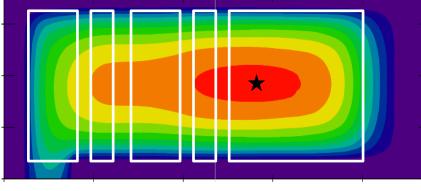

#### Twiddle Sensor: Potential Simulations

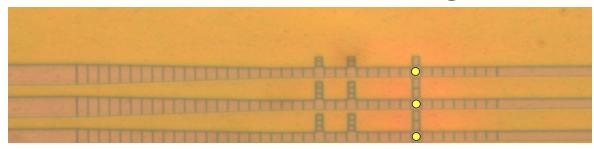

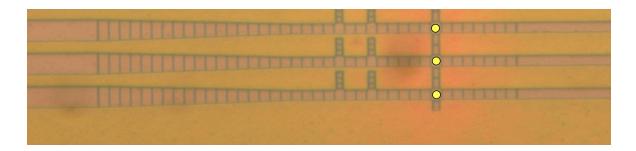

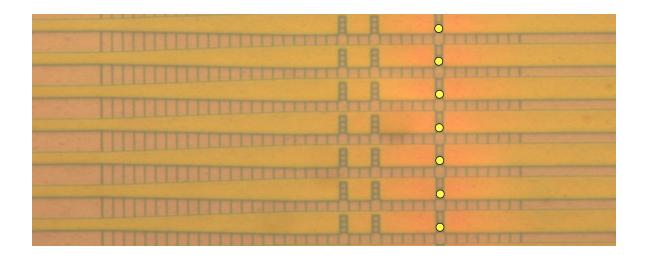

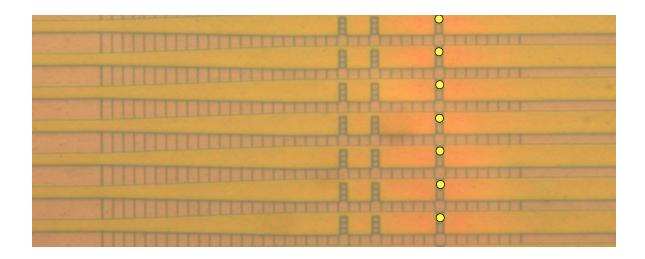

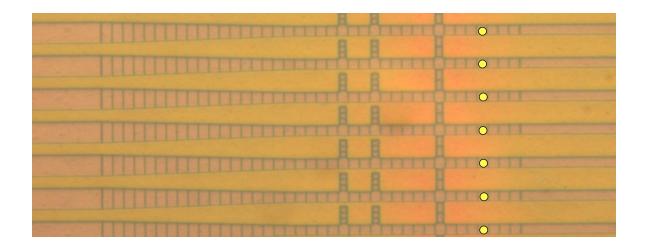

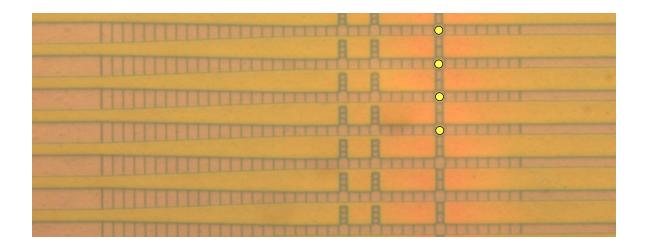

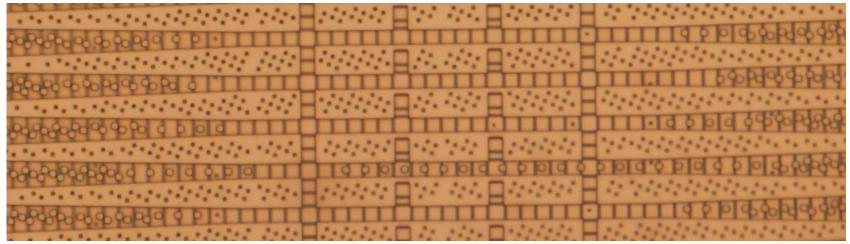

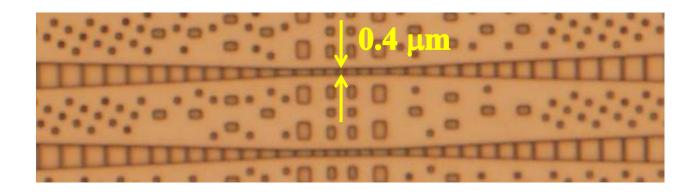

#### 3 um channels 2.5 um wide gates

Electrical potential in volts at the helium surface above the channels

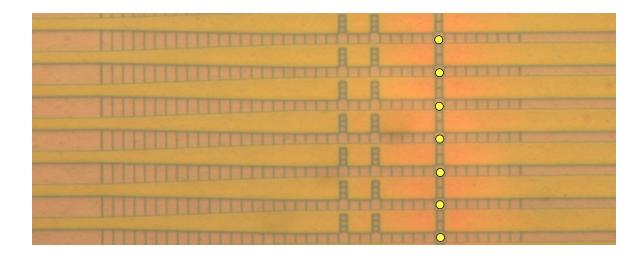

### Wider gates!!!

- 6 X 6 um Sense gate

- Gate in between Sense and Twiddle

Twiddle

Sense

### What do we do for our next chip???

- 1. Narrower channels (avoid filling)

- 2. Narrower gates (avoid cheesing)

- 3. Some wider gates (better sensing)

- 4. Turnstile